Conversor analógico a digital

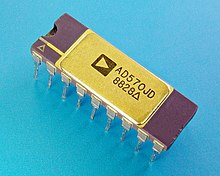

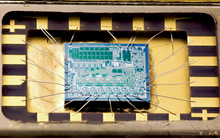

Un convertidor analógico-digital es un dispositivo electrónico, componente o parte de un componente para convertir señales de entrada analógicas en un flujo de datos digitales , que luego se pueden procesar o almacenar. Otros nombres y abreviaturas son ADC , análogo a digital del convertidor o convertidor A / D , Inglés ADC ( un nalogue-a- d IGITAL c onverter ) o poco A / D.

Se utilizan diversas técnicas de reposicionamiento. La contraparte es el convertidor de digital a analógico (DAU).

Los convertidores analógico-digitales son componentes elementales de casi todos los dispositivos en la electrónica moderna de comunicación y entretenimiento, como B. teléfonos celulares , cámaras digitales o videocámaras . También se utilizan para registrar valores medidos en sistemas de investigación y producción industrial, en máquinas y objetos técnicos cotidianos como vehículos de motor o electrodomésticos.

Manera de trabajar

Un ADC convierte una señal de entrada continua de tiempo y valor (señal analógica) en una secuencia discreta de tiempo y valor discreta de valores representados digitalmente. Debido a un número finito de posibles valores de salida, siempre hay una cuantificación . El resultado de una conversión AD se puede imaginar en un diagrama de tiempo de señal en una secuencia de puntos con distancias horizontales y verticales escalonadas. Los principales parámetros de un ADC son su profundidad de bits y su frecuencia de muestreo máxima . El tiempo de conversión suele ser mucho más corto que el recíproco de la frecuencia de muestreo.

La profundidad de bits de un convertidor AD ya limita la máxima precisión posible con la que se puede convertir la señal de entrada. La precisión utilizable es menor debido a otras fuentes de error en el ADC. Además de los métodos más rápidos posibles, también existen métodos lentos (de integración) para suprimir la interferencia.

Discretización de tiempo (muestreo)

La frecuencia de muestreo mínima necesaria para una discretización sin pérdidas resulta del ancho de banda de la señal de entrada.

Para poder reconstruir completamente la señal más tarde, la frecuencia de muestreo debe ser mayor que el doble de la frecuencia máxima posible en la señal de entrada (ver Frecuencia de Nyquist ). De lo contrario, hay un submuestreo y los cables en la señal reconstruida a la señal de entrada no son frecuencias existentes. Por lo tanto, la señal de entrada debe tener limitación de banda . O es esto por sí solo o se convierte en una señal de este tipo mediante un filtrado de paso bajo .

A veces, sin embargo, la señal que se va a muestrear es de tan alta frecuencia que esta condición no se puede implementar técnicamente. Sin embargo, si la señal de entrada es periódica, una reconstrucción aún puede ser posible mediante un muestreo múltiple con un desplazamiento de tiempo sin violar el teorema de muestreo, ya que los puntos intermedios se determinan cuando la señal pasa varias veces y, por lo tanto, un mayor número de puntos de interpolación. se crea, lo que al final da como resultado un aumento en la tasa de muestreo.

En muchos procesos de conversión, la señal de entrada no debe cambiar durante la conversión de señal. Luego cambie al convertidor AD real, un circuito de muestreo y retención (muestreo y retención) antes del cual el valor de la señal ( muestra en inglés ) análogo se almacena en caché que permanece constante durante la cuantificación. Esto es particularmente cierto para los convertidores paso a paso y bit a bit, que requieren tiempos de conversión más largos. Si un convertidor requiere este circuito de muestreo y retención, generalmente se incluye hoy cuando se implementa como un circuito integrado .

En muchas aplicaciones, la señal de entrada siempre debe muestrearse exactamente en los mismos intervalos de tiempo. Sin embargo, debido a variaciones aleatorias en las distancias, se produce un efecto que se conoce como jitter . Falsifica la señal original en la reconstrucción posterior, ya que nuevamente es equidistante, es decir, con los mismos intervalos de tiempo.

El tiempo de conversión no debe confundirse con la latencia de un convertidor, i. H. el tiempo que transcurre desde la adquisición hasta que ha pasado un convertidor AD en la fecha. Este tiempo puede ser mucho más largo que el tiempo de conversión, lo que puede resultar particularmente perjudicial en la tecnología de control. Es causado por la canalización del convertidor, el posprocesamiento de los datos y la transmisión de datos en serie .

Cuantización

La cuantificación de la señal previamente discreta en el tiempo representa la transición real de una señal analógica a una señal digital Debido a la profundidad de bits finita del convertidor, solo hay un cierto número de palabras de código y su voltaje de entrada asociado. La señal está cuantificada. La desviación entre el voltaje de entrada real y el voltaje de entrada cuantificado se denomina desviación de cuantificación . Cuantos más bits o palabras de código estén disponibles, menor será esta inevitable desviación. En un convertidor AD ideal, cada bit adicional reduce este ruido en 6,02 dB. Con convertidores AD reales, el número efectivo de bits (ENOB) se puede utilizar para estimar lo que aportaría un bit adicional en el convertidor en consideración (por ejemplo, un bit adicional en un convertidor de 12 bits con un ENOB de 11 bits sería aprox.0, 15 bits o 0,9 dB).

La relación entre el voltaje de entrada no distorsionado máximo posible y el ruido con una entrada sin señal se denomina rango dinámico . Los convertidores que entregan una palabra de código constante cuando no hay señal de entrada tienen un rango dinámico infinitamente alto. Tiene más sentido especificar la relación señal-ruido (o SINAD , relación señal-ruido y distorsión, relación de la señal a la suma de ruido y distorsión).

Valor de referencia

Dado que la señal analógica alimentada al ADC se convierte en un valor digital variable, debe evaluarse con un valor o señal especificada ( rango de señal de entrada o rango de medición ). En general, se utiliza un valor de referencia fijo (por ejemplo, una tensión de referencia generada internamente). La señal de entrada analógica se mapea digitalmente, la referencia define el valor pico permisible de la señal de entrada.

Curva de cuantificación

En los convertidores de analógico a digital, siempre existe una relación no lineal entre las variables de entrada y salida . Sin embargo, si el valor digital cambia a intervalos constantes con el aumento de la tensión de entrada o si la curva característica se aproxima a una línea recta con gradaciones extremadamente finas, se habla de un convertidor lineal analógico-digital. Existen

| Versiones unipolares, por ejemplo en el sistema dual. | ||

| 000… 000 para 0 | 100… 000 para / 2 | 111… 111 para - 1 LSB |

| Versiones bipolares, por ejemplo en el sistema dual con offset. | ||

| 000… 000 para / 2 | 100… 000 para 0 | 111… 111 para / 2 - 1 LSB |

También se pueden utilizar otras codificaciones, por ejemplo, el complemento a dos , el código BCD .

Interfaces

Además del circuito de muestreo y retención ya mencionado , se requieren más circuitos para la interfaz con el mundo analógico, por lo que a menudo se integran en un chip junto con el convertidor real. Estos pueden ser, por ejemplo, circuitos de búfer o amplificadores, posiblemente con ganancia conmutable ( amplificador de ganancia programable (PGA)) así como entradas para transmisión de señal diferencial . También hay variantes sin un amplificador de resta real en la entrada; En cambio, las dos líneas de la señal diferencial se procesan una tras otra y solo entonces se forma la diferencia (las llamadas entradas pseudo- diferenciales ).

Los datos digitales están disponibles en la salida. Clásicamente, cada bit de la variable de salida aparece en su propio pin de conexión; el tamaño se emite en paralelo , que no debe confundirse con la conversión en paralelo . Si el tamaño se va a mostrar en una pantalla , también se utilizan codificadores integrados de siete segmentos , o el tamaño se emite como un código BCD en un proceso multiplex . La desventaja de la salida en paralelo, especialmente cuando se procesa más con microprocesadores o controladores , es la gran cantidad de pines de conexión necesarios. Por lo tanto, las conexiones en serie se implementan a menudo , por ejemplo, con los protocolos I²C , SPI o I²S . Con velocidades de datos adecuadas, se utiliza , por ejemplo, la tecnología LVDS o JESD204B .

Desviaciones

Además del inevitable error de cuantificación, los convertidores AD reales tienen los siguientes errores:

Errores de punto cero, errores de ganancia y errores de no linealidad

Los siguientes errores se definen como desviaciones en las características entre el convertidor real e ideal (ver figura):

- Error de punto cero (compensación)

- Error de ganancia ( Inglés ganancia de error )

- Error de no linealidad

El error de ganancia a menudo se da como una fracción del valor actual, el error de punto cero junto con el error de cuantificación y el error de no linealidad como fracciones del valor final o como un múltiplo de un LSB.

Error en la graduación

Los pasos individuales pueden variar en ancho.

Con variables de entrada que aumentan continuamente, dependiendo del método de implementación, se puede omitir un valor de la variable de salida, especialmente si hay un arrastre de varios dígitos binarios, por ejemplo, de 0111 1111 a 1000 0000. Esto se conoce como "faltante códigos ”.

Errores temporales y de apertura

Tras la conversión de cada señal de entrada no constante del reloj del convertidor, Δ es provocada por fluctuaciones temporales t ( fluctuación de reloj ), un cambio temporal en el error proporcional de la señal de entrada. En el caso de una señal sinusoidal de frecuencia f y amplitud A, es . Cualquier fluctuación crea ruido adicional: no existe un umbral por debajo del cual no haya deterioro en la relación señal / ruido. Muchos convertidores actuales (especialmente los convertidores delta-sigma) tienen procesamiento de reloj interno. El trasfondo de esto es que muchos convertidores requieren una frecuencia de reloj interna más alta o, en el caso de los convertidores delta-sigma, esa fluctuación allí directamente (es decir, incluso con una señal de entrada constante) provoca errores de conversión.

Proceso de implementación

Hay una gran cantidad de métodos que se pueden utilizar para convertir señales analógicas en digitales. Los siguientes son los principios fundamentales. En todos los ejemplos, la tensión eléctrica se utiliza como variable de entrada.

Los propios bloques controlan el proceso interno de una conversión. Para la cooperación con una computadora, se puede proporcionar un ADC con una entrada de inicio para la solicitud de una nueva conversión, con una salida "ocupada" para la notificación de la conversión en curso y con salidas de datos compatibles con bus para leer el valor digital resultante.

Convertidor integrador (método de recuento)

Hay dos procesos involucrados en estos procedimientos:

- un proceso analógico influenciado por la variable medida, en el que un condensador se carga continuamente y se descarga de nuevo alternativamente,

- un proceso digital que mide tiempos o densidades de pulso dependiendo del proceso de carga, que se cuenta.

También se cuenta el convertidor de seguimiento. Funciona como un convertidor de retroalimentación sin condensador y se explica más adelante.

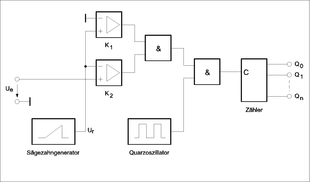

Convertidor de pendiente única (método de diente de sierra / rampa única)

En el método de diente de sierra, el voltaje de salida de un generador de diente de sierra se compara con el potencial de tierra (0 V) y el voltaje de entrada del ADC a través de dos comparadores K 1 y K 2 . Durante el período en el que la tensión de diente de sierra pasa a través del rango entre 0 V y la tensión , se cuentan los pulsos de un oscilador de cristal . Debido a la pendiente constante del voltaje de diente de sierra, el tiempo transcurrido y, por lo tanto, la lectura del contador al alcanzar es proporcional al nivel del voltaje de entrada del ADC. Al final del proceso de recuento, el resultado del recuento se transfiere a un registro y está disponible como señal digital. Luego, el contador se reinicia y comienza un nuevo proceso de traducción.

El tiempo de conversión de este ADC depende del voltaje de entrada. Las señales que cambian rápidamente no se pueden capturar con este tipo de convertidor. Los convertidores que utilizan el método de dientes de sierra son imprecisos, ya que el generador de dientes de sierra funciona con la ayuda de un condensador de integración dependiente de la temperatura y la edad. Debido a su complejidad de circuito relativamente baja, se utilizan para tareas simples, por ejemplo, en consolas de juegos para digitalizar la posición de un potenciómetro que se mueve mediante un joystick o un volante.

Convertidores duales y cuádruples (método de rampa múltiple)

Los convertidores de pendiente doble y cuádruple consisten esencialmente en un integrador y varios contadores e interruptores electrónicos . El integrador funciona con un condensador externo de alta calidad que se carga y descarga en dos o más ciclos. Con el procedimiento de dos rampas (pendiente doble), la entrada del integrador se conecta primero al voltaje de entrada del ADC desconocido y la carga se lleva a cabo durante un intervalo de tiempo fijo. Para la descarga posterior, el integrador se conecta a una tensión de referencia conocida de polaridad opuesta. Los detalles se explican en metrología digital . El tiempo de descarga necesario para alcanzar voltaje cero en la salida del integrador se determina mediante un contador; la lectura del medidor representa directamente el voltaje de entrada si está dimensionado apropiadamente. Con este método, el tamaño de la capacidad se reduce del resultado. Para corregir el error de punto cero del ADC, se lleva a cabo un ciclo de carga / descarga adicional con la entrada del integrador en cortocircuito con el método de cuatro rampas. La tensión de referencia es el factor determinante de la precisión; esto significa, por ejemplo, que deben evitarse las fluctuaciones inducidas térmicamente.

Dichos convertidores basados en el método de rampas múltiples son lentos, no requieren un circuito de muestreo y retención y ofrecen alta resolución, así como una buena linealidad diferencial y una buena supresión de señales de interferencia como ruido o acoplamiento de red. El campo de aplicación típico son los dispositivos de medición de pantalla ( multímetros digitales ), que apenas necesitan un tiempo de conversión inferior a 500 ms y, con un tiempo de integración adecuado, pueden eliminar las perturbaciones de 50 Hz superpuestas en la frecuencia de red.

Conversor de saldo de carga

En el proceso de equilibrio de carga , el condensador de un integrador se carga con una corriente eléctrica proporcional a la variable de entrada y se descarga mediante picos de corriente cortos en la dirección opuesta, de modo que no se acumula carga en promedio. Cuanto mayor es la corriente de carga, con mayor frecuencia se descarga. La frecuencia es proporcional a la variable de entrada; se cuenta el número de descargas en un tiempo fijo y proporciona el valor digital. En términos de su comportamiento, el proceso es similar al proceso de doble pendiente. Otras etapas de entrada analógicas que contienen un convertidor de tensión-frecuencia con un nivel de precisión suficientemente alto también conducen a un valor digital a través del recuento de frecuencia.

Convertidor de retroalimentación (proceso en serie)

Estos funcionan con una DAU que proporciona un valor de comparación . Esto se aproxima a la señal de entrada analógica utilizando una estrategia adecuada . El valor digital establecido al final de la DAU es el resultado del ADC. Dado que el proceso requiere un período de tiempo en el que la señal de entrada no debe cambiar, se toma una “muestra” mediante un circuito de muestreo y retención (S / H) y se registra durante la implementación.

Reubicador de seguimiento

Aquí se utiliza un contador como memoria de datos. Dependiendo del signo de , el sistema cuenta hacia arriba o hacia abajo en un paso y luego lo compara nuevamente, lo cuenta y lo compara nuevamente hasta que la diferencia es menor que el paso ajustable más pequeño. Estos convertidores simplemente "siguen" la señal, por lo que el tiempo de conversión depende de la distancia entre la señal de entrada actual y la señal durante la última conversión.

Aproximación sucesiva

Estos funcionan con una DAU que genera un valor de comparación cada vez. La señal de entrada está limitada mediante el anidamiento de intervalos . La aproximación sucesiva simple convierte un bit por paso. Se puede lograr una conversión que es órdenes de magnitud más precisa y más rápida si la conversión se lleva a cabo de forma redundante mediante la conversión con un tamaño de paso menor que el que corresponde a un bit.

Método de pesaje

Un posible método de aproximación es el método de pesaje . Primero, todos los bits se ponen a cero en una memoria de datos ( registro de aproximación sucesiva , SAR). Comenzando con el bit más significativo ( Bit más significativo , MSB) hasta el bit menos significativo, se reducirá al bit menos significativo (LSB) determinado uno tras otro todos los bits del valor digital.

La unidad de control establece el bit en curso a uno a modo de prueba; el convertidor de digital a analógico genera el voltaje de comparación correspondiente al valor digital actual. El comparador compara esto con el voltaje de entrada y hace que la unidad de control reinicie el bit en progreso a cero si el voltaje de comparación es mayor que el voltaje de entrada. De lo contrario, el bit es al menos necesario y permanece establecido. Después de establecer el bit menos significativo es más pequeño que el paso ajustable más pequeño.

La señal de entrada no debe cambiar durante la conversión, de lo contrario , los bits de orden inferior se obtendrían sobre la base de los bits de orden superior que se determinaron pero ya no son válidos. Por lo tanto, se conecta un circuito de muestreo y retención (S / H) aguas arriba de la entrada. El ADC necesita un tiempo de conversión de ciclo de reloj para cada bit de precisión. Dichos convertidores logran resoluciones de 16 bits a una tasa de conversión de 1 MHz.

Convertidores redundantes

Los convertidores de analógico a digital redundantes similares al proceso de pesaje suponen que no hay una reducción a la mitad exacta del intervalo todavía abierto alrededor del valor objetivo, pero que este intervalo sólo está limitado por una parte del mismo. Para ello, cuentan con un convertidor de digital a analógico, cuyos elementos no se clasifican según el sistema dual, es decir, siempre por un factor de 2, pero por un factor menor. Por un lado, acepta que se requieren más elementos para cubrir el mismo rango de valores, pero por otro lado, habilita al convertidor para trabajar un orden de magnitud más rápido y lograr una precisión que es varios órdenes de magnitud mayor: Cuanto más rápido La función proviene del hecho de que el comparador En cada paso, no tiene que esperar hasta que su amplificador se haya estabilizado en un múltiplo de la precisión objetivo (siempre en el orden de magnitud de tantas constantes de tiempo de establecimiento como se supone que el convertidor convierte bits ), sino tomar una decisión después del corto tiempo de asentamiento del 50 por ciento que luego es defectuoso en un área bastante grande dentro del intervalo restante. Sin embargo, esto es más que absorbido por los elementos convertidores de diseño redundante. El tiempo de conversión total de dicho convertidor es del orden de magnitud una potencia de diez por debajo del de su modelo simple. Debido al proceso de implementación redundante, dicho convertidor tiene un nivel mucho más bajo de ruido inherente que su contraparte puramente dual.

Además, dicho ADC puede calibrarse a sí mismo, hasta una precisión que solo está limitada por el ruido. Al dejar que la autocalibración se ejecute mucho más lentamente que la implementación en la aplicación práctica, la influencia del ruido en este proceso se puede reducir en un orden de magnitud. La curva característica resultante de dicho convertidor es absolutamente lineal, salvo una desviación similar a un ruido de unos pocos múltiplos del elemento más pequeño utilizado para la autocalibración. Al colocar dos de estos convertidores uno al lado del otro en el mismo chip y uno siempre en el modo de calibración, dichos convertidores pueden hacerse casi resistentes a las tolerancias de fabricación, cambios de temperatura y voltaje de funcionamiento. La resolución alcanzable está exclusivamente limitada por ruido.

Método Delta-Sigma

El método delta-sigma, también conocido como convertidor de 1 bit, se basa en la modulación delta-sigma . En su forma más simple (modulador de primer orden), la señal de entrada llega al integrador a través de un restador analógico y genera una señal en su salida, que es ponderada con uno o cero por un comparador. Un flip-flop genera una señal binaria discreta en el tiempo con la que un convertidor de digital a analógico de 1 bit suministra un voltaje eléctrico positivo o negativo, lo que hace que el integrador vuelva a cero a través del sustractor ( bucle de control ). Un filtro digital descendente convierte el flujo de bits en serie y de alta frecuencia en datos con una frecuencia de actualización baja, pero un ancho de bits grande (16 o 24 bits) y una relación señal / ruido alta (94 a 115 dB). En la práctica, los convertidores delta-sigma se construyen como sistemas de tercer o cuarto orden, es decir, mediante varias etapas diferenciales e integradoras dispuestas en serie. Esto permite una mejor configuración del ruido y, por lo tanto, una mayor ganancia de resolución con el mismo sobremuestreo.

Una ventaja del convertidor delta-sigma es que la dinámica se puede intercambiar dentro de ciertos límites debido al ancho de banda. Debido al muestreo continuo en la entrada, no se requiere ningún circuito de muestreo y retención. Además, se hacen pocas exigencias al filtro anti-aliasing analógico.

Las ventajas se pagan por la desventaja de la latencia comparativamente alta, que se debe principalmente a las etapas de filtrado digital. Por lo tanto, los convertidores Delta-Sigma se utilizan cuando se requieren curvas de señal continuas y solo se requieren anchos de banda moderados, como en el sector de audio. Prácticamente todos los dispositivos de audio del sector de la electrónica de entretenimiento, como las grabadoras DAT , utilizan estos convertidores.

También se utiliza cada vez más para convertidores de datos en tecnología de comunicación y tecnología de medición debido a la caída de precios. Sin embargo, debido al alto sobremuestreo requerido para esto, el método tiene sus límites a frecuencias más altas. El límite es de alrededor de 2,5 MHz.

Convertidor paralelo

Convertidores en paralelo de una etapa (convertidores flash)

Mientras que la aproximación sucesiva realiza varias comparaciones con un solo comparador, el método directo o implementación Flash puede hacerlo con una sola comparación. En el caso de los convertidores flash, sin embargo, se requiere un comparador implementado por separado para cada valor de salida posible (excepto para el más grande). Por ejemplo, un convertidor flash de 8 bits requiere 2 8 −1 = 255 comparadores.

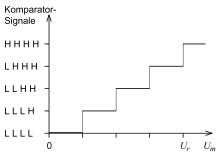

Todos los comparadores comparan simultáneamente la señal de entrada analógica en el convertidor flash con los valores de comparación (generados por un divisor de voltaje lineal). A esto le sigue una conversión de código de las 2 n −1 señales del comparador en un código binario de n bits de ancho (con n : resolución en bits). El resultado está disponible inmediatamente después de los retrasos de procesamiento (tiempo de conmutación de los comparadores y retraso en la lógica de decodificación). Como resultado, los convertidores flash son muy rápidos, pero generalmente también implican altas pérdidas de energía y costos de adquisición (especialmente con las altas resoluciones).

Independientemente de la resolución, la conversión de código solo requiere una columna con puertas AND y una columna con puertas OR (ver imagen). Convierte el resultado de los comparadores en un número binario. Funciona con un retardo de tránsito muy corto que es el mismo para todos los dígitos binarios. Se requieren tres comparadores para los cuatro valores posibles de un convertidor de dos bits. El cuarto solo tiene la función de señalar que se ha excedido el rango de medición y apoyar la conversión del código.

Convertidores en paralelo de varias etapas (convertidores de canalización)

Los convertidores de tubería son convertidores analógico-digitales de etapas múltiples con varias etapas independientes que se construyen en una arquitectura de tubería . Sus etapas suelen consistir en convertidores flash de unos pocos bits.

Se lleva a cabo una cuantificación aproximada en cada etapa de la tubería, este valor se convierte en una señal analógica con un DAC y se resta de la señal de entrada almacenada temporalmente. El valor residual se alimenta cada vez más a la siguiente etapa. La ventaja radica en el número muy reducido de comparadores, p. Ej. B. 30 para un convertidor de ocho bits de dos etapas. Además, se puede lograr una resolución más alta. La etapa múltiple aumenta la latencia, pero no reduce significativamente la frecuencia de muestreo. Los convertidores de tubería han reemplazado a los convertidores en paralelo reales, excepto en aplicaciones de tiempo extremadamente crítico. Estos convertidores multinivel alcanzan velocidades de datos de 250 MSPS (megamuestras por segundo) con una resolución de 12 bits (MAX1215, AD9480) o una resolución de 16 bits con 200 MSPS (ADS5485).

Los valores de los niveles de cuantificación se suman teniendo en cuenta su ponderación. La mayoría de las veces, una ROM de corrección también contiene datos de calibración que se utilizan para corregir errores que surgen en las etapas de digitalización individuales. En algunas versiones, estos datos de corrección también se generan en respuesta a una señal externa y se almacenan en una RAM .

Los convertidores de canalización se utilizan normalmente en todos los osciloscopios digitales y al digitalizar señales de vídeo. Como ejemplo, el MAX109 permite una frecuencia de muestreo de 2,2 GHz con una resolución de 8 bits. Mientras tanto, sin embargo, hay convertidores aún más rápidos (4 GSPS) y más precisos (16 bits a 1 GSPS). En los osciloscopios digitales actuales con posibles velocidades de muestreo de 240 GSPS, los demultiplexores también están conectados en sentido ascendente.

Convertidor híbrido

Un convertidor híbrido no es un convertidor independiente, sino que combina dos o más métodos de conversión, por ejemplo, basado en una estructura SAR, con el comparador original siendo reemplazado por un convertidor flash. Esto significa que se pueden determinar varios bits simultáneamente en cada paso de aproximación.

Situacion del mercado

Básicamente, existen cuatro procesos en el mercado:

- Los convertidores de tubería se utilizan para altas tasas de muestreo. Velocidades de 40 MSPS a 5 GSPS. Dinámica habitual de 8 bits, 12 bits (hasta 4 GSPS) o 16 bits (hasta 1 GSPS).

- Si es importante una alta precisión a velocidades de muestreo moderadas y la latencia no es un problema, se utilizan convertidores delta-sigma. Velocidades desde unos pocos PLC hasta 2,5 MSPS. Profundidades de bits de 16 bits a 24 bits.

- Si la latencia es significativa o perturba el comportamiento de paso bajo comparativamente empinado, se utilizan convertidores de aproximación sucesiva. Velocidades de 0,1 MSPS a 10 MSPS.

- En dispositivos de medición de pantalla simples, como multímetros, se utilizan métodos de conteo de amortiguación de interferencias lentos, como convertidores de doble pendiente.

Con este procedimiento puede cubrir casi todos los requisitos prácticos y con requisitos moderados (por ejemplo, 12 bits, 125 KSPS, 4 canales), estos convertidores se pueden obtener de forma económica (aproximadamente 1 €).

Parámetros importantes

- Muestreo (frecuencia de muestreo): indicación de la frecuencia de transposición.

- Resolución (Resolución): ancho de los pasos (número par de etapas o número de puntos), que se utilizan para mostrar la señal de salida.

- Error de punto cero : la característica del convertidor (sin tener en cuenta la gradación) se desplaza. El valor digital difiere del valor correcto en una cantidad constante.

- Error de sensibilidad , error de ganancia: la característica del convertidor (sin tener en cuenta la gradación) está torcida (error de gradiente). El valor digital se diferencia del valor correcto en un porcentaje constante de la variable de entrada.

- No linealidad integral : el error que surge del hecho de que una curva característica del convertidor, que se toma como una base lineal (sin tener en cuenta la gradación), no es recta.

- No linealidad diferencial : desviación del ancho de las etapas de conversión entre sí

- Curva de cuantificación : representación gráfica de la relación entre los valores de salida digital y los valores de entrada analógica, p. Ej. B. siguiendo un curso lineal o logarítmico .

- Error de cuantificación : debido a la resolución limitada, la señal de salida se desvía de la curva funcional (continua).

- Brecha de información (código faltante): si un aumento continuo en la señal de entrada no da como resultado valores numerados consecutivamente del código de salida, pero se omite un valor; posible con una no linealidad diferencial de más de 1 LSB.

- Latencia : retardo de propagación desde la adquisición de la señal de entrada hasta la provisión de la señal de salida asociada.

- Relación señal / ruido en dB

- Rango dinámico en dB

- Parámetros dinámicos

- Interferencia de intermodulación en dB

- Corriente de funcionamiento: cuanto más rápido tenga que trabajar la electrónica del convertidor, mayor será su corriente de suministro (autocalentamiento).

Ver también

- Antialiasing (procesamiento de señales)

- Dithering (tecnología de audio)

- Tecnología de medición digital

- Analizador multicanal

- Lista de términos de audio

literatura

- Rudy J. van de Plassche: convertidores CMOS de analógico a digital y de digital a analógico integrados. 2ª edición. Kluwer Academic, Boston 2003, ISBN 1-4020-7500-6 (inglés)

- Ulrich Tietze, Christoph Schenk: Tecnología de circuitos semiconductores. 12ª edición. Springer, Heidelberg 2002, ISBN 3-540-42849-6

- Rüdiger Klein, La nueva electrónica de libros de trabajo. Bercker, Kevelaer, ISBN 978-3-645-65094-6

enlaces web

- Literatura sobre convertidores de analógico a digital en el catálogo de la Biblioteca Nacional Alemana

- Conceptos básicos basados en simulaciones

- Introducción a los convertidores delta-sigma

- Convertidor AD en "Microelectrónica aplicada" - Conceptos básicos

- ADC de subrango canalizados (PDF; 1 MB)

Evidencia individual

- ↑ De los términos habituales que se utilizan aquí son los que se han especificado para ingeniería por estandarización en DIN 1319-2 .

- ↑ Application Note 1108 - Understanding Single-Ended, Pseudo-Differential and Fully-Differential ADC Inputs , nota de aplicación de Maxim Integrated , 2002-006-14, consultado el 12/12/2018

- ↑ Ficha técnica del convertidor flash MAX109 (PDF; 452 KiB).